# LOONGSON 2F

PRELIMINARY DATA

# High performance 64bit superscalar MIPS microprocessor

### FEATURES

- 64-bit MIPS III Instruction Set and Extended Set compatible, 64-bit word length;

- Quad-issue dynamic superscalar with support for 2 fix point units, 2 fully pipelined floating point multipliers / adders and a load / store unit.

- 9-10 stage super pipelining with support for register renaming, dynamic scheduling, branch prediction and other out-of-order execution.

- IEEE 754-compatible floating-point units enable fully pipelined multiplication and addition arithmetic operation, and hardware division and extraction, with support for media acceleration.

- The joint TLB has 64 entries each of which contains

2 pages ranging from 4KB-4MB; the independent

16-32 entry instruction TLBs support executable

bits and prevents buffer overflow attack.

- On-chip separate our-way set associative L1 caches offer 64 KB capacity and 62-byte block for code and data application respectively.

- 512KB of on-chip four-way set associative L2 cache (32-byte block) can be turned on/off by software.

- Integrated 64-bit DDR3 memory controller I/F at 333MHz max.

- Integrated 133MHz PCIX bus controller, with support for PCIX bus, and compatible with PCI.

6/27/2007

- 1-GHz main frequency allows for dynamic frequency conversion and shutdown of the core clock for dynamic power management.

- Lower power < 5W at 1GHz.</li>

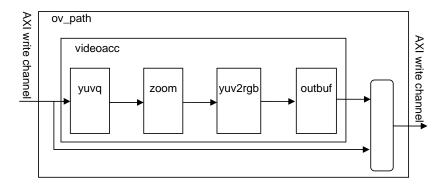

- Video accelerate module in its write data path to PCI/PCI-X controller. With software driver, the video accelerate module can transfer YUV format video data to RGB format and do zoom action automatically.

#### OVERVIEW

The Loongson2F is an evolution of the Loongson2E with the enhanced I/O and memory accessing bandwidth and a software work frequency changing scheme and compatibility to MIPS64.

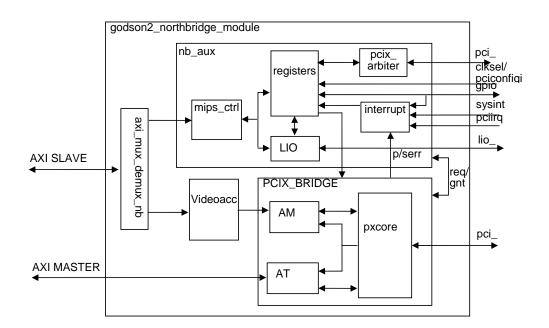

The Loongson2F integrates a high performance Loongson2 CPU core, DDR2 memory controller, PCI/PCI-X interface, Local bus, interrupt controller and video acceleration unit.

The Loongson2F will be manufactured in CMOS090 90nm technology using standard rules.

1/82

This is preliminary information on a new product in development or undergoing evaluation. Details are subject to change without notice

Rev 0.1

批注 [S1]: MAIN Features, Review and add/remove if needed.

批注 [S2]: Overview summary

# 1. Product Overview

The Loongson2F is an evolution of the Loongson2E with the enhanced I/O and memory accessing bandwidth and a software work frequency changing scheme and compatibility to MIPS64.

The Loongson2F has a standard 32-bit PCI/PCI-X interface, a standard 64-bit DDR2 interface, an 8/16bit Local IO interface, a 4-bit GPIO interface and an enhanced processor core developed from Loongson2E.

The Loongson2F is intended to be build into a system via standard PCI/PCI-X bus. It can both act as a master or a target PCI/PCI-X as device/host.

The Loongson2F is also intended to achieve higher memory accessing bandwidth by utilizing a 64-bit DDR2 memory controller.

The Loongson2F is expected to have better power management ability by using a software manageable work frequency changing scheme. The operating system can utilize this feature to change the processor frequency according to the workload.

The Loongson2F integrates a video accelerate module in its write data path to PCI/PCI-X controller. Accompany with software driver, the video accelerate module can transfer YUV format video data to RGB format and do zoom action automatically. This can greatly reduce the processor's work load when the system utilizes a simple VGA controller.

The cores are centered on 2x2 AXI cross bar with 128-bit width data bus. The CPU core and PCI/PCI-X slave takes up two master ports, DDR2 controller one slave port, and all other modules including the PCI/PCI-X master share one slave port.

| DDR2      | CPU core<br>PCIX Bridge                          |  |  |  |  |  |

|-----------|--------------------------------------------------|--|--|--|--|--|

|           | cross bar                                        |  |  |  |  |  |

| registers | interrupt Local IO video accelarate PCIX arbiter |  |  |  |  |  |

### 1.1 CPU Core

Loongson2F CPU core is a four-issue nine-stage general-purpose RISC microprocessor that

implements the 64-bit MIPS instruction set.

The features of this CPU core include:

- Four issue

- Nine stage

- Out of order executing

批注 [S3]: Detail overview of the G2F

批注 [S4]: This block diagram is not details enough.

- Two fix-point units

- Two float-point units

- 64-entry reorder buffer

- 24-entry load-store queue

- 16-entry fix-point issue queue

- 16-entry float-point issue queue

- 64-entry data TLB

- 8-entry instruction TLB

- 64KB instruction L1 cache, 4way set associative

- 64KB data L1 cache, 4way set associative

- 512KB L2 cache, 4way set associative

- 2K-entry BHT

- 32-entry BTB

### 1.2 AXI Crossbar

The AXI Crossbar provides a 2x2 interconnection compatible with the AMBA AXI protocol. The features of the crossbar include:

- 128bit, full-pipelined data-path.

- Up-to-4 asynchronous FIFOs to transfer signals between different clock domains.

- Up-to-4 programmable address windows for individual AXI Master.

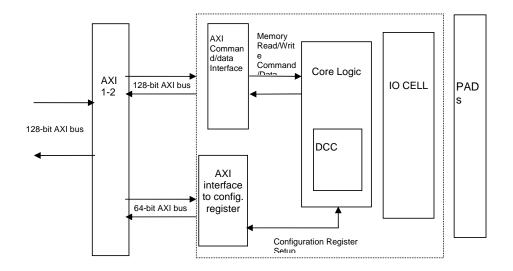

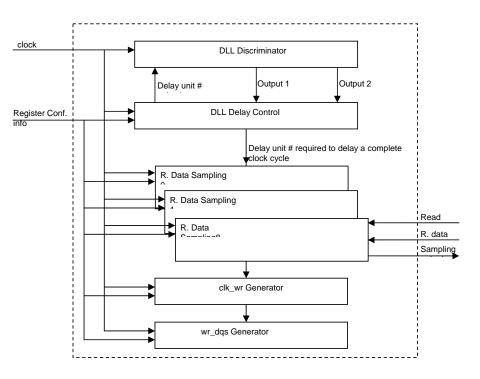

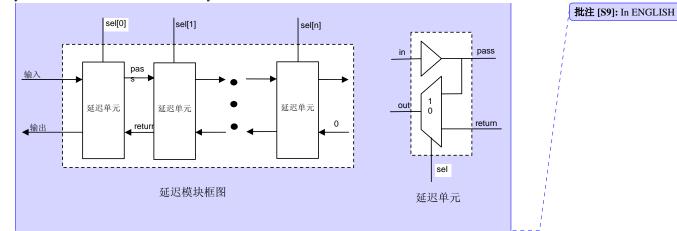

### 1.3 DDR2 SDRAM Controller

The built-in memory controller of Loongson2F processor fully conforms to DDR SDRAM industry

standard JESD79C. All memory read/writes are implemented according to JESD79C specification.

The features of this memory controller include:

- Fully pipelined command read and writes data interfaces to the memory controller.

- Advanced bank look-ahead features for high memory throughput.

- Interface to a standard AXI port.

- A programmable register interface to control memory device parameters and protocols including auto pre-charge.

- Full initialization of memory on memory controller reset.

- Built-in adjustable Delay Compensation Circuitry (DCC) for reliable data sends and captures timing.

- ECC functionality with single-bit and double-bit error reporting and automatic correction of single-bit

error events. Programmable reporting and correction. Programmable removal of ECC storage.

- Programmable memory data path size of full memory data width or half memory data width.

- Clock frequencies form 113MHZ to 333MHZ supported.

#### 1.4 Video Accelerator

The Video Accelerator supports the standard yuv444 and yuv422 video format. With the cooperation of software, the data of YUV format can be translate to RGB format. Besides, Video Accelerator can perform auto-zoom with little software intervention.

#### 1.5 PCI/PCI-X Controller

The PCI/PCI-X controller conforms to both PCI 2.3 and PCI-X 1.0 specification. Its features include:

- Pin selectable host or satellite mode

- 32-bit bus width

- Support fast back to back as a target

- Support dual address cycle

- 8 outstanding master request

- 4 delay-split read request

- Support PCI-X 133

#### 1.6 PCI/PCI-X Arbiter

The PCI/PCI-X arbiter follows both PCI and PCI-X specification. Including following features:

- Two-level round-robin arbitration theme

- Bus parking

- Bad device detect and isolation

#### 1.7 Local Bus

The local bus provides a simple bus interface for system boot ROM and IO device. The interface is designed for chip-connect simplicity.

### **1.8 Interrupt Controller**

12 pins are available for chip interrupt. Including 4 dedicated interrupt pin, 4 PCI interrupts and 4 GPIO capable of interrupt triggering. Each pin can be individually configured as level/edge sensitive and masked out.

# 2. SoC Architecture

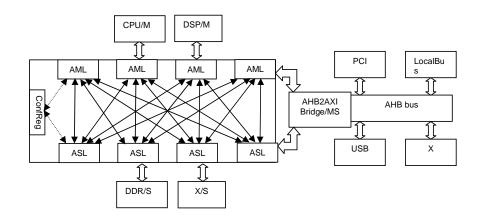

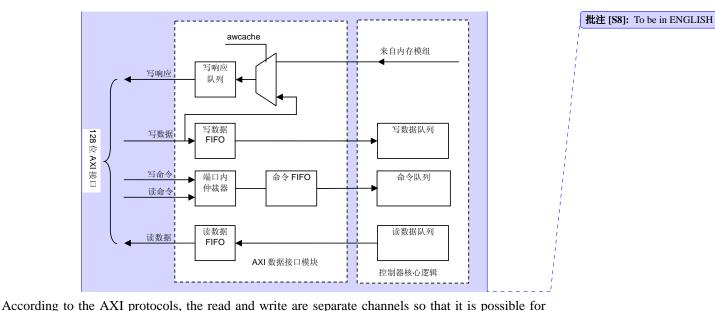

The expandable Loongson SoC architecture consists of two stages: the crossbar switch which interfaced with high-performance IP blocks such as Loongson 2x, DSP, DDR2, PCI Express; and the share bus which is connected with low-speed IP blocks such as Loongson 1x, PCI and Local Bus. The Loongson SoC adopts the AXI interface specification for its crossbar switch ports and AHB standard for its share bus interfaces. The AHB bus is connected with the AHB2AXI Bridge, as a standard AXI interface, as shown in the figure below.

This architecture offers scalability and configurability. Fist of all, the number of ports is configurable for both the AXI crossbar switch and the AHB bus. The AXI stage supports up to 4 master AXH devices which can be a Loongson 2x, a DSP (codec IP), a AHB master port and a high-speed I/O such as PCE Express or Hyper Transport; and up to 4 slave AXI devices which can be a AHB slave port, a DDR2 port, a high-speed I/O port such as PCI Express or Hyper Transport and other high-speed ports. Second, individual ports are configurable in synchronous or asynchronous transmission mode, thus eliminating the problem on signal transmission due to the clock domain crossing (CDC), to meet the requirements of other IP blocks. Further more, parameters including FIFO items and arbitration logic are dynamically configurable according to the specific features of other IP blocks.

Its core architecture includes three sections: the crossbar switch in the AXI interface (AXI switch module), the bridge between AXI and AHB (AXI2AHB) and the AHB bus and its arbiter (AHB module). Only AXI switch module is available in the L2F.

批注 [S5]: From your doc More details about the architecture. I think it is good to keep the comparison to L2E. But we need to have a identical L2E document.

### 2.1 AXI Switch Module

The AXI switch module is connected to IP blocks via AXI interfaces, with built in arbitration and routing logic. Seeing the diversity trend of IP blocks, special attention is paid to the design of the arbitration and addressing logic in terms of customization of hardware specification and software programmability. One AXI master may access multiple slaves. For example, a CPU core needs to access DDR, PCI and other interfaces. In turn, a slave may be accessed by multiple masters. For example, a DDR interface can be accessed by a CPU core, PCI master and other IP blocks. Typically, Master IP blocks have well-established specifications for interfaces. However, some slave IP blocks have some certainties in interface specifications, like the configurable number of AXI interfaces, built-in arbitration logic, etc.

The AXI Switch Module consists of AML (AXI-Master-Link) and ASL (AXI-Slave-Link). The module also includes a register module used for software-management/-configurability of AML and ASL sumodules. The AML is connected with the Master using AXI Slave specifications, which provides buffer and addressing. It requires a corresponding software-configurable register to configure address windows that match accessible AXI Slaves in one-to-one and multiple-to-one mode. The AML will decode and select based on the address windows. The address space is determined by the base address, size and local base address. With 4 segments of address pace at most, one AML needs 12 registers. The ASL is connected with the Slave through the AXI Master specifications, providing arbitration and Slave service requests. The register module receives write and read requests on configuration of the registers of the AXI Switch Module, such configuration of address windows in the AML module. The AXI specifications define that every AXI interface has five channels: a Read Address, a Read Data, a Write Address, a Write Date and a Write Response. All the channels have the same 128-bit data width, 64-bit address width, and 8-bit ID width. The ID includes global ID which is determined by structure and interconnected logic, and local ID which is internally decided by the master IP. While allowing for multiple masters and requests, and out-oforder completion, the ASL uses ID to determine the address route along which data will return. The ID itself contains logic and topology information that is transparent to slave IPs. How to assign and manage ID:

- 1. Master IP starts a new transaction, when the AXI interface ID contains only local ID information. The AML sends the local ID domain to the ASL.

- 2. After receiving the transaction, the ASL uses the logic and topology to determine the global ID and put it together with the local ID. Then the resulting ID is transmitted to the

slave IP.

- 3. The slave IP returns the data with an ID to ASL. In turn, the ASL sends the ID to the AML that corresponds to the global ID domain.

- 4. The AML masks and returns the global ID to the Master  $IP_{\circ}$

In the above process, the master adopts the address mode. The assignment of global ID is transparent to the master.

The relationship between the AML and ASL is asker and server. The interface signaling still uses the AXI interface specifications. The AML buffers a request from the AXI master until next data beat comes when it determines the destination ASL port based on the access address. The ASL responds to a read/write request from a AML through the arbitration. The communication between AML and ASL is consistent with the interface in terms of data, address, and ID bit-width. Because the AML and ASL are interconnected with a crossbar switch, the signals from all the AML ports are delivered to four ASL ports simultaneously. For convenience of identification, the signals between the four AXL ports and the four master devices are prefixed with m0\_, m1\_, m2\_, m3\_; these between the four slave devices and AXI switch, with s0\_, s1\_, s2\_, s3\_; these from the AML to ASL, with aml0\_, aml1\_, aml2\_, aml2\_; these from the four ASL to AML, with asl0\_, asl1\_, asl2\_, asl3\_. The Loongson SoC architecture AXI bus signals are named in small letters.

## 2.1.1 AML Design

The AML buffers a write/read request from the AXI master and then decides the corresponding ASL module based on the configurable address windows. Each AML contains 4 window addresses each of which are software-configured to correspond to a certain AXI slave. The address decoding logic transmits the request to the corresponding ASL. The window address is configurable as low as 1MB, for a minimum number of address bits to compare. The Loongson SoC architecture has a 128-bit AXI data width (max), resulting in 128-bit of write data buffer.

To decouple the AXI master and AXI switch pipelines, the AML provides a two-item buffer request queues for read and write requests respectively. A request from the AXI crossbar switch pipeline first joins the request queue, and then one of the items is transmitted to the corresponding ASL after windows comparison.

### 2.1.2 ASL Design

Similarly, the interface between the ASL and AML implements AXI protocols, with separate channels and arbitration logic for read and write requests. After the arbitration process, the ASL buffers and transmits a request from various AML modules to the AXI slave.

The response from the AXI slave is buffered at the ASL for beat before going to the AML for arbitration. The corresponding AML port is identified immediately since the response signal contains the requesting AXI master ID. Similarly, the there are two items in the buffer when the ASL receives a response from the AXI slave.

### 2.1.3 Asynchronous Interface

For an asynchronous interface, the clock signal converts between the AML and ASL. Multiple asynchronous request sources are synchronized to the slave clock domain for arbitration. So the ASL and AXI slave share the same clock source. The request from different clock domains are processed at the AML module which share the same clock source with the master. Before interoperating with the ASL, the AML signal has to be synchronized with the ASL by an asynchronous FIFO. Repeat the same process when data returns. With the overhead of asynchronous signal conversion, a higher FIFO depth might be needed to minimize the loss in performance. The FIFO is configurable in bit width and depth at RTL level.

### 2.1.4 Access Sequence

The AXI switch has no constraints on read sequence and enables out-of-order execution. However, because the write address and data are traveling along different paths, the some of the buffer channels could be locked up without limitations. Therefore some limitations are imposed on the master write operation. According to the AXI protocol, the slave supports the master out-oforder write by limiting the depth of out-of-order write or the number of out-of-order write operations. The master out-of-order write is forbidden when there is no available slave information. In other words, the master is required to transfer the write address in the same sequence as the write data, of course, without need for simultaneity. Now our masters are designed for the same sequence. Actually, both the write addresses and the write data are put in position beforehand, even at the same time, thus eliminating the need for out-of-order transfer. However, in our crossbar switch, the slave port receives and transmits write from 4 masters and transfers to the slave IP blocks. For the slave, this is a type of out-of-order write that takes place among multiple masters. Some support is needed to avoid the lockup effect. For example, when Master 1's write address arrives earlier than

# 51

its write data, it seizes one of the buffer entries in the slave port. If only one entry is available, the slave port will not receive other write address but wait for the corresponding write data. Just then Master 2's write data arrives and enters the slave port. Now the crossbar switch cannot transmit to the slave IP block. It has no more available buffer entry to receive Master 1's write data it is awaiting, either. The lockup takes place.

Solving this problem, the Loongson SoC builds a write operation list at the slave port of the AXI crossbar switch, which is used to control the reception and transmission of write data, preventing the buffer in the slave side from seizing by the write data that the slave IP block is not ready to receive. This is done by recording all the write address requests that the slave IP block have received to this write operation list and allowing the write data matching these recorded requests to enter the slave section of the crossbar switch, ensuring all these write data are received by the slave IP block without taking up the buffer in the slave section of the switch. Once the last write data request arrives, these write operations are deleted from the write operation list, thus overcoming the lockup due to out-of-order writes among different masters.

## 2.1.5 Bridge Module for Data Width Conversion

The crossbar switch reaches 128 bits in both the AXI interface and internal data width in consideration of: a) today, all the memory modules sold in the market are 64-bit DDR/DDR2, so 128-bit data is returned per beat. The adoption of 128-bit data width makes it possible to prevent the delay occurred when the CPU accesses the memory because of the data width conversion; b) So far the L2x provides 64 bit of access channels for (L1 and registers as well as L1 and L2), which is scalable to 128 bits at most. For this reason, 128-bit bandwidth is sufficient; c) a 128-bit crossbar switch offers moderate performance and high cost-effectiveness, compared with lower 64-bit and expensive 256-bit bandwidth.

An IP block with data width higher or lower than 128 bits has to connect to the AXI crossbar switch module through a bridge module where its data width is converted to standard 128 bits required by the AXI switch. The bridge module, which provides data width conversion and protocol translation, is available in master-link interfacing to AXI master and slave link interfacing to AXI slave. The data width conversion scenarios include:

- A request higher than 128 bits from the AXI Master can be transferred in the Burst mode including multiple Transfers as defined in the AXI specifications.

- A request lower than 128 bits from the AXI Master can be assigned a transfer size using the SIZE Zone of the AXI protocol.

- The return data higher than 128 bits from the AXI Slave can be transferred in the Burst

mode including multiple Transfers as defined in the AXI specifications.

• When return data from the AXI Slave is lower than 128 bits, the allocation of the data on the 128-bit data bus is determined by the transfer address.

When the AXI Master (L2x) has to convert its data path width from 128 bits at the AXI Switch to 32 bits at the AXI Slave (PCI), LEN and SIZE conversions are needed at the AXI Slave. Typically, in order to link modules with different data path widths, the bridge module needs a specific queue for data width conversion.

### 2.1.6 Configuration Register Module

This module allows for configuration of address window registers. These windows each include three 64-bit registers: BASE which is aligned to MB (megabyte), MASK which adopts a format similar to the netmask with a high level of 1, and MMAP where the two low levels represent the number of the appropriate ASL. The assignment of these configuration registers is done using 64-bit two-word write operation.

Window Hit Formula: (IN\_ADDR & MASK) == BASE

Target Port Number: MMAP [1:0] in hit window

New Address Conversion: OUT\_ADDR = (IN\_ADDR & ~MASK) | {MMAP [63:20], 20'h0}

| Address   | Name         | Description                         |

|-----------|--------------|-------------------------------------|

| 3ff0 0000 | M0_WIN0_BASE | base address of Window 0 of Mater 0 |

| 3ff0 0008 | M0_WIN1_BASE | base address of Window 1 of Mater 0 |

| 3ff0 0010 | M0_WIN2_BASE | base address of Window 2 of Mater 0 |

| 3ff0 0018 | M0_WIN3_BASE | base address of Window 3 of Mater 0 |

| 3ff0 0020 | M0_WIN0_SIZE | Mask of Window 0 of Mater 0         |

| 3ff0 0028 | M0_WIN1_SIZE | Mask of Window 1 of Mater 0         |

| 3ff0 0030 | M0_WIN2_SIZE | Mask of Window 2 of Mater 0         |

| 3ff0 0038 | M0_WIN3_SIZE | Mask of Window 3 of Mater 0         |

| 3ff0 0040 | M0_WIN0_MMAP | Mapped base address of Window 0 of  |

|           |              | Master0                             |

| 3ff0 0048 | M0_WIN1_MMAP | Mapped base address of Window 1 of  |

|           |              | Master0                             |

| 3ff0 0050 | M0_WIN2_MMAP | Mapped base address of Window 2 of  |

|           |              | Master0                             |

| 3ff0 0058 | M0_WIN3_MMAP | Mapped base address of Window 3 of  |

|           |              | Master0                             |

| 3ff0 0060 | M1_WIN0_BASE | base address of Window 0 of Mater 1 |

| 3ff0 0068 | M1_WIN1_BASE | base address of Window 1 of Mater 1 |

| 3ff0 0070 | M1_WIN2_BASE | base address of Window 2 of Mater 1 |

| 3ff0 0078 | M1_WIN3_BASE | base address of Window 3 of Mater 1 |

| 3ff0 0080 | M1_WIN0_SIZE | Mask of Window 0 of Mater 1         |

57

| 2000 0000   | MI WINII CUZE |                                                            |

|-------------|---------------|------------------------------------------------------------|

| 3ff0 0088   | M1_WIN1_SIZE  | Mask of Window 1 of Mater 0                                |

| 3ff0 0090   | M1_WIN2_SIZE  | Mask of Window 2 of Mater 1                                |

| 3ff0 0098   | M1_WIN3_SIZE  | Mask of Window 3 of Mater 1                                |

| 3ff0 00a0   | M1_WIN0_MMAP  | Mapped base address of Window 0 of                         |

|             |               | Master1                                                    |

| 3ff0 00a8   | M1_WIN1_MMAP  | Mapped base address of Window 1 of                         |

|             |               | Master1                                                    |

| 3ff0 00b0   | M1_WIN2_MMAP  | Mapped base address of Window 2 of                         |

|             |               | Master1                                                    |

| 3ff0 00b8   | M1_WIN3_MMAP  | Mapped base address of Window 3 of                         |

|             |               | Master1                                                    |

| 3ff0 00c0   | M2_WIN0_BASE  | base address of Window 0 of Mater 2                        |

| 3ff0 00c8   | M2_WIN1_BASE  | base address of Window 1 of Mater 2                        |

| 3ff0 00d0   | M2_WIN2_BASE  | base address of Window 2 of Mater 2                        |

| 3ff0 00d8   | M2_WIN3_BASE  | base address of Window 3 of Mater 2                        |

| 3ff0 00e0   | M2_WIN0_MASK  | Mask of Window 0 of Mater 2                                |

| 3ff0 00e8   | M2_WIN1_MASK  | Mask of Window 1 of Mater 2                                |

| 3ff0 00f0   | M2_WIN2_MASK  | Mask of Window 2 of Mater 2                                |

| 3ff0 00f8   | M2_WIN3_MASK  | Mask of Window 3 of Mater 2                                |

| 3ff0 0100   | M2_WIN0_MMAP  | Mapped base address of Window 0 of                         |

|             |               | Master2                                                    |

| 3ff0 0108   | M2_WIN1_MMAP  | Mapped base address of Window 1 of                         |

| 0110 0100   |               | Master2                                                    |

| 3ff0 0110   | M2_WIN2_MMAP  | Mapped base address of Window 2 of                         |

| 5110 0110   |               | Master2                                                    |

| 3ff0 0118   | M2_WIN3_MMAP  | Mapped base address of Window 3 of                         |

| 5110 0110   |               | Master2                                                    |

| 3ff0 0120   | M3_WIN0_BASE  | base address of Window 0 of Mater 3                        |

| 3ff0 0128   | M3_WIN1_BASE  | base address of Window 1 of Mater 3                        |

| 3ff0 0120   | M3_WIN2_BASE  | base address of Window 2 of Mater 3                        |

| 3ff0 0138   | M3_WIN3_BASE  | base address of Window 2 of Mater 3                        |

| 3ff0 0140   | M3_WIN0_MASK  | Mask of Window 0 of Mater 3                                |

| 3ff0 0148   | M3_WIN1_MASK  | Mask of Window 1 of Mater 3                                |

| 3ff0 0150   | M3_WIN2_MASK  | Mask of Window 2 of Mater 3                                |

| 3ff0 0158   | M3_WIN3_MASK  | Mask of Window 2 of Mater 3<br>Mask of Window 3 of Mater 3 |

| 3ff0 0158   | M3_WIN0_MMAP  | Mapped base address of Window 0 of                         |

| 5110 0100   |               | Mapped base address of window 0 of<br>Master 3             |

| 3ff0 0168   | M3_WIN1_MMAP  | Mapped base address of Window 1 of                         |

| 5110 0108   |               | Mapped base address of window 1 of<br>Master 3             |

| 3ff0 0170   | M3_WIN2_MMAP  | Mapped base address of Window 2 of                         |

| 5110 01 /0  |               | Mapped base address of window 2 of<br>Master 3             |

| 3ff0 0178   | M2 WIN2 MMAD  | Mapped base address of Window 3 of                         |

| 5110 01 / 8 | M3_WIN3_MMAP  | Mapped base address of window 5 of<br>Master 3             |

|             | L             | 11/13/01 3                                                 |

In addition, when none of the four address windows is hit because of reading an invalid address caused by CPU's speculation execution, to prevent the system from crashing, the configuration register module return all-zero data to the CPU.

# 2.2. AXI2AHB Bridge

Not available on L2F.

# 2.3. AHB Bus Module

Not available on L2F.

# 3. Processor Core Improvement

批注 [S6]: Samecomments. From your doc. Improvement vs L2E. Details comments on the 4 main improvements

The L2F's processor core features great architecture improvement, including:

a) Optimized power consumption by minimizing unwanted bit flipping of register stacks, L1 and L2 Caches and other flip-flops and by using dynamic frequency conversion logic to reduce the power consumption when the CPU is free;

b) MIPS compatible design. Compatible with MIPS III, the L2F has to move some of custom operations to SPECIAL 2 and COP2's custom operation code space;

c) AXI compatible processor interfaces.

d) Performance improvement through allowing cache block replacement command to be executable in user mode, as well as partial delay optimization.

# **3.1 Optimized Power**

The L2F delivers lower power by minimizing unwanted bit flipping of register stacks, L1and L2 Caches, and using dynamic frequency conversion logic designs.

The reduced bit flipping is achieved by refusing to read on the register stacks when the instruction operand is 0 or immediate. In the L2E, two operands are read from the register stacks for each instruction. They are src1 and scr2. Our study shows about 70% of fixpoint instruction src2 uses immediate or 0 for operand and this is true of 10-30% of src1. It is necessary to read on the register stacks at the operand of immediate or zero. In this way, the L2F determines whether Read Enable of the register stack should be activated by judging the operand immediate or zero.

The same way is applied in L1 Cache to reduce the undesired read operations to the cache. In the L2E, if the load/store bus (dmemref) is valid, the CPU can read from 16 blocks of RAM of 4 cache banks simultaneously. Each RAM is 512×64 in size. In contrast, L2F allows for more refined access to reduce unnecessary read to reduce power consumption, including:

- Typical store is done in dmemref through simple access to the tag section, without need of access to the data section.

- Typical load is done in dmemref through simple access to the appropriate 64 bits instead of the whole 256 bits of each bank, or by access to only four blocks of cache RAM per cycle.

- CACHE25 is done in dmemref by accessing only four blocks of cache RAM per cycle.

- CACHE1 and CACHE21 are done in dmemref through reading all the 16 blocks of cache RAM per cycle.

- REPLACE and LOOKU are done in drefill through access to all the 16 blocks of cache RAM per cycle.

This supplicated control of RAM Read Enable provides around 80% power reduction for L1 cache RAM.

For reducing the power consumption of L2 cache, L2f includes an additional software-controlled L2 cache Read Enable/Disable, which is implemented through adapting scache and cache2mem, the two modules of the processor core: a) scache: when L2 cache is available, the inclusion relation between L2 and L1 caches ensures the cache block written back from L1 is hit in L2 cache. When L2 cache is disabled, a replacement from L1 cache and a writeback incurred due to L1 cache instruction have to be copied out through the arbiter module. When L2 cache is disabled, if the bit of dmemwrite\_w is dirty, then after one beat, the data and address are transferred from the dmemwrite bus to the smemwrite bus which, the write request bus of the cache RAM, provides replacement/writeback for the L2, and provides the same function for the L1 when the L2 is disabled. b) cache2mem: when L2 is disabled, the L1 internal request is put into SCMISS mode immediately after going into the missqueue. Without the need to issue a find (LOOKUP) or writeback and invalid (WTBKINV) request to the L1, diwtbkcntis set at 11. Similarly, without the need to refill the L2, srefillent is set at 11.

For software compatibility, when the L2 is disabled, the Loognson 2F support the L2 cache instructions, which, however is not executable. After entering the missqueue, the L2 cache instructions are set in the RDY, with the srefillent set at 11. In the RDY state, the chip sends a message along the refill bus to the CPO queue that appropriate instructions has been executed. If the L2 cache is disabled, it is necessary to determine whether the replacement in the data cache can be written back to the arbiter module (without write buffer) or the buffer (with the buffer). The signal wait\_cache\_yes is generated depending on whether the writeback incurred by the L1 instruction can be copied to the arbiter module (without write buffer) or the buffer (with the buffer). This signal will be zero only if the queue is empty and write is allowed without any ongoing writeback.

Furthermore, a thorough study shows the availability of flip-flops that can use pipeline enable signals for input enable control in the Loongson 2F. So thousands of such flip-flops are optimized for pipeline enable signal application.

The Loongson 2F is still designed with dynamic frequency conversion logic, making it possible to

reduce power consumption by scaling the main frequency when the OS is not in use. Controlled by software, the processor core runs at 0/8, 2/8, 3/8, 4/8, 5/8, 6/8, 7/8 and 8/8 of operating frequency. It is achieved by maintaining div\_count, a 8-bit shift counter at the PLL output clock which can dynamically adjust the number of 1 within the device based on a 3-bit control signal freq\_scale. When freq\_scale=011, for example, the processor core clock runs at 4/8 of the PLL clock frequency, and there are four shifting"1s" in the 8-bit div\_count. The core clock is the result of an individual bit of div\_count NAND the PLL clock phase.

# **3.2 MIPS Compatible Design**

MIPS only defined the user mode instructions in its early MIPS Architectures such as MIPS I, MIPS II, MIPS III, MIPS IV and MIPS V. Later the company provided both user mode and kernel mode in their new specifications such as MIPS32 and MIPS64. Now MIPS only licenses and supports MIPS32 and MIPS64.

MIPS compatibility is a main goal of the Loongson 2F design. It is designed to compatible with MIPS III. Implementing all the features described in the MIPSIII, Loongson 2E has some of custom instructions occupied the MIPS-reserved instruction slot. So in the 2F, these custom-tailored instruction opcodes need to remove to the user instruction slot (COP2 or Special2). They include instructions as follows:

- The 2E implemented MOVZ and MOVN, the instructions designed for MIPS IV instead of MIPS III. Compatible with MIPS64 specifications, eliminating the need of modifications.

- The media instructions take the COP2 slot reserved for user, compared with the 2E whose COP1 instruction slot is taken up.

- The MIPS architecture implements floating-point multiply-add instructions in MIPS IV and later versions, while the 2E realizes the floating-point multiply-accumulate instructions because the multiply-add is not available in MIPS III, resulting in incompatibility. For the 2F, the floating-point multiply-accumulate opcode need to remove to Special 2, the customer-reserved slot.

- In the 2E, the fmt domain for fixpoint instruction paired-single is used by media instructions, leading to incompatibility with MIPS. Align the 2F.

- Considering the fixpoint multiply-division instructions use HI and LO registers in the previous MIPS instruction set, the 2E implements the instruction using general-purpose registers for target registers. Remove these opcode to Special 2 instruction slot in the 2F.

Finally, these changes in instruction format do not impact the 2F's internal opcode and data paths. For example, the 2F uses COP2 slot for media instruction, but internally continues to use COP1 opcode slot and data paths.

### 3.3. AXI-Compatible Interface Design

The Loongson 2F implements extendable SoC interconnection architecture and L2 cache with configurable Enable/Disable using the AXI interface specifications. To achieve these features, we have to modify cache2mem, a module of the processor core.

The configurable Enable/Disable is realized adding a disable\_scache signal to the L2 cache. If the value of the signal is 1, the L2 cache is disabled; otherwise, the L2 is available. When the initial value of disable\_scache equals 0, this feature can be dynamically configured through OS.

In the Loongson SoC architecture, the processor core operates as a master and implements the AXI interface specifications. The AXI interface protocols include five channels: read address, read data, write address, write data and write response. The 2E incorporates the suncache, smemread, smemwrite, srefill0 and srefill1 buses into the five AXI channels.

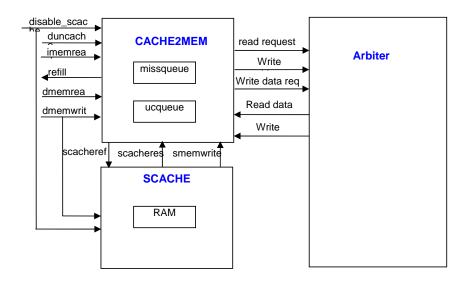

In the 2F, suncache's read and smemread are merged into the read address channel; suncache's write and smemwrite are merged, with write address separate from write data, into write address channel and write data channel; srefill0 and srefill1 combined into read data channel. In the Loongson SoC architecture, all the channels share a uniform data width of 128 bits, the same address width of 64 bits and ID length of 8 bits. The processor core is also modified in terms of domain widths. The diagram below provides the connection between CACHE2MEM, SCACHE and Arbiter.

51

# 3.4. Performance Optimization

During the implementation of Loongson 2E's Java virtual machine, it was found that great time was needed in refreshing the cache, and much of the time was consumed during system call (because cache instruction belongs to kernel instruction set, user code has to read the cache through system call). Therefore, a bit called user\_mode\_cacheop (DIAG [8]) is included in the DIAG control register of the 2F. When the bit is set to 1, the user mode program is allowed to use the cache refresh instructions (CACHE1、CACHE17、CACHE21...).

In addition, some of the delays are optimized for the 2F's physical paths. The delay-optimized section is mainly included in the CPU0 and fixpoint queues, dealing with forward speculation cancel.

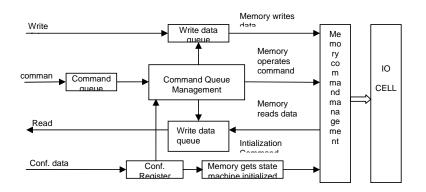

# 4. DDR2 SDRAM Memory Controller Design

## 4.1. Overview

The 2F integrates a built-in memory controller fully compatible with DDR2 SDRAM standard (JESD79-2B). Its main features as follows:

- Fully pipelined instruction, read/write on the interface

- Fusion and sort of memory instructions for higher overall bandwidth.

- Standard AXI Interface

- Configuration register read/write ports enable changes in basic memory parameters

- Built-in dynamic delay compensation (DCC) circuit for higher data transmission and reception reliability.

- ECC that detects 1-bit error and 2-bit error on the data path and automatically corrects 1-bit error.

- Operation frequency range: 133MHz-333MHz

# 4.2. Memory Control ASIC Interface and Memory Interface Signal

The memory control ASIC interface signals include AXI-certified interface signal, control signal and DDR2 SDRAM memory interface signal. Two additional pins are included for higher read accuracy. For signal definitions, see the table below:

| Name           | I/O        | Description                     |

|----------------|------------|---------------------------------|

| Memory Control | oller ASIC | Interface Signals (AXI Section) |

| aclk           | Ι          | AXI interface clock             |

| areset         | Ι          | AXI interface reset             |

| arid[7:0]      | Ι          | Read request ID                 |

| araddr[39:0]   | Ι          | Read request address            |

| arlen[3:0]     | Ι          | Read request length             |

| arsize[3:0]    | Ι          | Read request size               |

| arburst[1:0]   | Ι          | Read request burst type         |

| arvalid        | Ι          | Read request valid              |

| arready        | 0          | Read request ready              |

| rid[7:0]       | 0          | Read data ID                    |

| rdata[127:0]   | 0          | Read data                       |

| rresp[1:0]     | 0          | Read data response              |

| rlast          | 0          | Read last data indication       |

| rvalid         | 0          | Read data valid                 |

| rready         | Ι          | Read data reception ready       |

| awid[7:0]      | Ι          | write request ID                |

| awaddr[39:0]   | Ι          | write request address           |

| awlen[3:0]     | Ι          | write request length            |

批注 [S7]: This chapter will not be present in L2E documents.

| 1 10 01                 | т        | · ·                                            |

|-------------------------|----------|------------------------------------------------|

| awsize[3:0]             | Ι        | write request size                             |

| awburst[1:0]            | Ι        | write request burst type                       |

| awcache[3:0]            | Ι        | write request cache mode                       |

| awvalid                 | I        | write request valid                            |

| awready                 | 0        | write request reception ready                  |

| wid[7:0]                | Ι        | write data ID                                  |

| wdata[127:0]            | Ι        | write data                                     |

| wstrb[3:0]              | Ι        | write data strobe                              |

| wlast                   | Ι        | Write last data indication                     |

| wvalid                  | Ι        | write data valid                               |

| wready                  | 0        | write data ready                               |

| bid[7:0]                | 0        | Write response ID                              |

| bresp[1:0]              | 0        | Write response type                            |

| bvalid                  | 0        | Write response valid                           |

| bready                  | Ι        | Write response reception ready                 |

| Memory Controller       | ASIC Int | erface Signals (Control Signal Section)        |

| controller_int          | 0        | Memory controller interrupt output             |

| dll_lock                | 0        | Memory controller DLL lock indication          |

| ecc_dataout_corrected   | 0        | ECC 1-bit error indication (corrected)         |

| ecc_dataout_uncorrected | 0        | ECC 2-bit error indication (uncorrected)       |

| q_almost_full           | 0        | Command queue full indication                  |

| refresh_in_process      | 0        | Memory module in process of refresh indication |

| srefresh_enter          | Ι        | Memory module enters self-refresh control      |

| scanen                  | Ι        | Test mode enable                               |

| scanin                  | Ι        | Test input                                     |

| scanout                 | 0        | Test output                                    |

| scanmode                | Ι        | Test mode select                               |

| test_rd_clk             | Ι        | Test read clock input                          |

| test_wr_clk             | Ι        | Test write clock input                         |

| param_75_ohm_sel        | 0        | Controller Pad termination resistor select     |

| tsel                    | 0        | Controller termination resistor enable         |

| config_reg_enable       | Ι        | configuration register access control          |

# Memory Controller DDR Interface Signals

| dq[72:0]   | IO | DDR2 SDRAM data bus               |

|------------|----|-----------------------------------|

| dqs[8:0]   | IO | DDR2 SDRAM data strobe            |

| dqs_n[8:0] | IO | DDR2 SDRAM reverse data strobe    |

| dqm[8:0]   | 0  | DDR2 SDRAM data mask              |

| addr[14:0] | 0  | DDR2 SDRAM address bus            |

| ba[2:0]    | 0  | DDR2 SDRAM Bank address           |

| we#        | 0  | DDR2 SDRAM write enable           |

| cas#       | 0  | DDR2 SDRAM column select enable   |

| ras#       | 0  | DDR2 SDRAM row select enable      |

| cs[3:0]#   | 0  | DDR2 SDRAM chip select            |

| cke[1:0]   | 0  | DDR2 SDRAM clock enable           |

| clk[5:0]   | 0  | DDR2 SDRAM noninvert clock output |

| clk_n[5:0] | 0 | DDR2 SDRAM invert clock output                |

|------------|---|-----------------------------------------------|

| odt[3:0]   | 0 | DDR2 SDRAM onchip terminating resistor select |

| gatein     | Ι | Data reception indication                     |

| gateout    | 0 | Data reception indication                     |

# 4.3. Memory Controller Configuration Registers

The memory controller includes 26 64-bit configuration registers. One register contains data that may form multiple parameters, a single parameter or only partial parameter. The table below provides these configuration registers and their parameter information (all the unused bits are reserved).

| Parameter Name                 | Bit     | Defau<br>lt | Range   | Description                                               |  |  |  |  |

|--------------------------------|---------|-------------|---------|-----------------------------------------------------------|--|--|--|--|

| CONF_CTL_00[31:0] Offset: 0x00 |         |             |         |                                                           |  |  |  |  |

|                                |         |             |         | Issue an auto refresh command to                          |  |  |  |  |

| AREFRESH                       | 24      | 0x0         | 0x0-0x1 | memory based on the                                       |  |  |  |  |

|                                |         |             |         | auto_refresh_mode parameter setup                         |  |  |  |  |

| AP                             | 16      | 0x0         | 0x0-0x1 |                                                           |  |  |  |  |

| ADDR_CMP_EN                    | 8       | 0x0         | 0x0-0x1 | Allow command requeueing logic to check address conflict? |  |  |  |  |

|                                |         |             |         | Record the ageing commands in the                         |  |  |  |  |

| ACTIVE_AGING                   | 0       | 0x0         | 0x0-0x1 | queue avoiding starvation of low                          |  |  |  |  |

|                                |         |             |         | priorities?                                               |  |  |  |  |

| CONF_CTL_00[63:32] Off         | set: 0x | 00          |         |                                                           |  |  |  |  |

| DDR2_SDRAM_MODE                | 56      | 0x0         | 0x0-0x1 | Memory Controller DDRI and DDRII                          |  |  |  |  |

| DDR2_SDRAW_WODE                | 50      | 0.00        | 070-071 | mode setup                                                |  |  |  |  |

|                                |         |             |         | Allow controller auto precharge one                       |  |  |  |  |

| CONCURRENTAP                   | 48      | 0x0         | 0x0-0x1 | bank while issuing a command to                           |  |  |  |  |

|                                |         |             |         | another bank?                                             |  |  |  |  |

| BANK_SPLIT_EN                  | 40      | 0x0         | 0x0-0x1 | Allow command requeueing logic to                         |  |  |  |  |

|                                | 70      | ONO         | UNU UNI | split banks?                                              |  |  |  |  |

| AUTO_REFRESH_MODE              | 32      | 0x0         | 0x0-0x1 | Select when to issue an auto-precharge,                   |  |  |  |  |

|                                |         |             |         | next burst or command boundary?                           |  |  |  |  |

| CONF_CTL_01[31:0] Offse        | et: 0x1 | 0           |         |                                                           |  |  |  |  |

| ECC_DISBALE_W_UC_E             | 24      | 0x0         | 0x0-0x1 | Disable ECC when an unrecoverable                         |  |  |  |  |

| RR                             |         |             |         | error is found in R/M/W?                                  |  |  |  |  |

| DQS_N_EN                       | 16      | 0x0         |         | Enable DQA difference?                                    |  |  |  |  |

| DLL_BYPASS_MODE                | 8       | 0x0         |         | Enable DLL BYPASS Mode?                                   |  |  |  |  |

| DLLLOCKREG                     | 0       | 0x0         | 0x0-0x1 | Indicate if DLL locks? (Read only)                        |  |  |  |  |

| CONF_CTL_01[63:32] Off         | set: 0x | :10         |         |                                                           |  |  |  |  |

|                                |         |             |         | Is a mandatory write check required? If                   |  |  |  |  |

| FWC                            | 56 0x0  | 0x0         | 0x0-0x1 | yes, memory controller will store in                      |  |  |  |  |

|                                |         | 0.40        |         | memory XOR of value and data                              |  |  |  |  |

|                                |         |             |         | specified in the xor_check_bits.                          |  |  |  |  |

| FAST_WRITE                  | 48      | 0x0 | 0x0-0x1 | Allow controller to enable fast write? If<br>yes, controller will issue a write<br>command to memory module before<br>receiving complete write data.                                                      |

|-----------------------------|---------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENABLE_QUICK_SREFR<br>ESH   | 40      | 0x0 | 0x0-0x1 | Enable quick self-refresh? If yes,<br>memory will do self-refresh even if<br>initialization does not end.                                                                                                 |

| EIGHT_BANK_MODE             | 32      | 0x0 | 0x0-0x1 | Indicate if memory module has 8 banks.                                                                                                                                                                    |

| CONF_CTL_02[31:0] Offs      | et: 0x2 | 20  |         | F                                                                                                                                                                                                         |

| NO_CMD_INIT                 | 24      | 0x0 | 0x0-0x1 | Issue other commands over tDLL time during memory initialization?                                                                                                                                         |

| INTRPTWRITENA               | 16      | 0x0 | 0x0-0x1 | Interrupt previous read command with<br>autoprechagre plus other read/write<br>commands to the same bank?                                                                                                 |

| INTRPTREADA                 | 8       | 0x0 | 0x0-0x1 | Interrupt previous read command with<br>autoprechagre plus other read<br>commands to the same bank?                                                                                                       |

| INTRPTAPBURST               | 0       | 0x0 | 0x0-0x1 | Interrupt current autoprecharge with other commands to another bank?                                                                                                                                      |

| CONF_CTL_02[63:32] Of       | fset: 0 | x20 |         |                                                                                                                                                                                                           |

| PRIORITY_EN                 | 56      | 0x0 | 0x0-0x1 | Enable command requeue logic to prioritize?                                                                                                                                                               |

| POWER_DOWN                  | 48      | 0x0 | 0x0-0x1 | If yes, memory controller will close all<br>the memory pages with precharge<br>command to set clock enable low<br>without transmitting all the received<br>commands until this value is set back to<br>0. |

| PLACEMENT_EN                | 40      | 0x0 | 0x0-0x1 | Enable command requeue logic?                                                                                                                                                                             |

| <br>ODT_ADD_TURN_CLK_<br>EN | 32      | 0x0 | 0x0-0x1 | Insert a turn-around clock between the fast back-to-back read or write commands to different chip selects?                                                                                                |

| CONF_CTL_03[31:0] Off       | set: 0x | 30  |         | · · · · ·                                                                                                                                                                                                 |

| RW_SAME_EN                  | 24      | 0x0 | 0x0-0x1 | Allow command requeue logic to requeue write/read commands to the same bank?                                                                                                                              |

| REG_DIMM_EN                 | 16      | 0x0 | 0x0-0x1 | Enable registered DIMM memory module?                                                                                                                                                                     |

| REDUC                       | 8       | 0x0 | 0x0-0x1 | Only use 32-bit data path?                                                                                                                                                                                |

| PWRUP_SREFRESH_EXI<br>T     | 0       | 0x0 | 0x0-0x1 | Use self-refresh to exit power-down mode rather than memory initialization command?                                                                                                                       |

| CONF_CTL_03[63:32] Of       | fset: 0 | x30 |         |                                                                                                                                                                                                           |

| SWAP_PORT_RW_SAME<br>_EN    | 56      | 0x0 | 0x0-0x1 | Determine if the similar commands are<br>swapped on the same port when<br>swap_en is enabled?                                                                                                             |

| SWAP_EN                     | 48      | 0x0 | 0x0-0x1 | Swap a new highly prioritized command for an ongoing one when command                                                                                                                                     |

|                                 | 10       |     |         | requeue logic is enabled?                                                                               |  |

|---------------------------------|----------|-----|---------|---------------------------------------------------------------------------------------------------------|--|

| START                           | 40       | 0x0 |         |                                                                                                         |  |

| SREFRESH                        | 32       | 0x0 | 0x0-0x1 | Self-refresh memory?                                                                                    |  |

| CONF_CTL_04[31:0] Off           | set: 0x4 | 10  |         |                                                                                                         |  |

| WRITE_MODEREG                   | 24       | 0x0 | 0x0-0x1 | Write EMRS register of memory module?                                                                   |  |

| WRITEINTERP                     | 16       | 0x0 | 0x0-0x1 | Define if a write burst can be interrupted by a read command.                                           |  |

| TREF_ENABLE                     | 8        | 0x0 | 0x0-0x1 | Enable self refresh inside the controller?                                                              |  |

| TRAS_LOCKOUT                    | 0        | 0x0 | 0x0-0x1 | Issue auto-prechareg before the expiration of tRAS?                                                     |  |

| CONF_CTL_04[63:32] Of           | fset: 0  | x40 |         | · •                                                                                                     |  |

| RTT_0                           | 57:24    | 0x0 | 0x0-0x3 | Define the on-chip termination resistance of memory module.                                             |  |

| CTRL RAW                        | 49:48    | 0x0 | 0x0-0x3 | Set ECC detect and correction mode.                                                                     |  |

| AXI0_W_PRIORITY                 | 41:40    | 0x0 | 0x0-0x3 | Set priority for AXI0 port write command.                                                               |  |

| AXI0_R_PRIORITY                 | 33:32    | 0x0 | 0x0-0x3 | Set priority for AXI0 port read command.                                                                |  |

| CONF_CTL_05[31:0] Off           | set: 0x5 | 50  |         |                                                                                                         |  |

| COLUMN_SIZE                     | 26:24    | 0x0 | 0x0-0x7 | Set margin between actual and max (14) numbers of column addresses.                                     |  |

| CASLAT                          | 18:16    | 0x0 | 0x0-0x7 | Set CAS latency value.                                                                                  |  |

| ADDR_PINS                       | 10:8     | 0x0 | 0x0-0x7 | Set margin between actual and max (15) numbers of address pins.                                         |  |

| RTT_PAD_TERMINATIO<br>N         | 1:0      | 0x0 | 0x0-0x3 | Set termination resistance for memory controller pad                                                    |  |

| CONF_CTL_05[63:32] O            | ffset: 0 | x50 |         |                                                                                                         |  |

| Q_FULLNESS                      | 58:56    | 0x0 | 0x0-0x7 | Define a limit to the number of<br>commands beyond which memory<br>controller queue is considered full. |  |

| PORT_DATA_ERROR_TY<br>PE        | 50:48    | 0x0 | 0x0-0x7 | Define data error type on the memory controller ports.                                                  |  |

| OUT_OF_RANGE_TYPE               | 42:40    | 0x0 | 0x0-0x7 | Define the type of out-of-range access errors.                                                          |  |

| MAX_CS_REG                      | 34:32    | 0x4 | 0x0-0x4 | Define the number of chip-selects used in controller.                                                   |  |

| CONF_CTL_06[31:0] Off           | fset: 0x | 60  |         |                                                                                                         |  |

| TRTP                            | 26:24    | 0x0 | 0x0-0x7 | Define the number of cycles from memory read command to precharge.                                      |  |

| TRRD                            | 18:16    | 0x0 | 0x0-0x7 | Define the interval of the Active command to different banks                                            |  |

| TEMRS                           | 10:8     | 0x0 | 0x0-0x7 | Define emrs during memory initialization.                                                               |  |

| ТСКЕ                            | 2:0      | 0x0 | 0x0-0x7 | Define minimum CKE pulse width.                                                                         |  |

| CONF_CTL_06[63:32] Offset: 0x60 |          |     |         |                                                                                                         |  |

| APREBIT                         | 59:56    | 0x0 | 0x0-0xf | Define which bit of address line is                                                                     |  |

| F                               | ·I       |     |         | •                                                                                                       |  |

|                      |           |     |         | cale stad to some disutant and shares to                                                                          |

|----------------------|-----------|-----|---------|-------------------------------------------------------------------------------------------------------------------|

|                      |           |     |         | selected to send autoprecharge to memory.                                                                         |

| WRLAT                | 50:48     | 0x0 | 0x0-0x7 | Define the time (based on clock cycles)<br>from transmission of write command to<br>reception of first data.      |

| TWTR                 | 42:40     | 0x0 | 0x0-0x7 | Define the required clock cycles from write to read command.                                                      |

| TWR_INT              | 34:32     | 0x0 | 0x0-0x7 | Define write recovery time for memory module.                                                                     |

| CONF_CTL_07[31:0] 0  | ffset: 0x | 70  |         |                                                                                                                   |

| ECC_C_ID             | 27:24     |     | 0x0-0xf | Define source ID number for 1-bit ECC error.                                                                      |

| CS_MAP               | 19:16     | 0x0 | 0x0-0xf | Define available chip-selects                                                                                     |

| CASLAT_LIN_GATE      | 11:8      | 0x0 | 0x0-0xf | Define the time (measured in a half of a cycle) for which gate open is active when the read command returns data. |

| CASLAT_LIN           | 3:0       | 0x0 | 0x0-0xf | Define CAS Latency for memory module.                                                                             |

| CONF_CTL_07[63:32] ( | Offset: 0 | x70 | I       |                                                                                                                   |

| MAX_ROW_REG          | 59:56     | 0xf | 0x0-0xf | Define the actual number of row addresses.                                                                        |

| MAX_COL_REG          | 51:48     | 0xe | 0x0-0xe | addresses.                                                                                                        |

| INITAREF             | 43:40     | 0x0 | 0x0-0xf | Define the number of autorefresh<br>commands required for system<br>initialization.                               |

| ECC_U_ID             | 35:32     | 0x0 | 0x0-0xf | Define the source ID for unrecoverable<br>dual-byte errors. (Translator's Note: 2-<br>bit errors?)                |

| CONF_CTL_08[31:0] O  | ffset: 0x | 80  |         |                                                                                                                   |

| ODT_RD_MAP_CS3       | 27:24     | 0x0 | 0x0-0xf | Make its ODT termination resistance<br>available in defining CS3 read<br>command?                                 |

| ODT_RD_MAP_CS2       | 19:16     | 0x0 | 0x0-0xf | Make its ODT termination resistance<br>available in defining CS2 read<br>command?                                 |

| ODT_RD_MAP_CS1       | 11:8      | 0x0 | 0x0-0xf | Make its ODT termination resistance<br>available in defining CS1 read<br>command?                                 |

| ODT_RD_MAP_CS0       | 3:0       | 0x0 | 0x0-0xf | Make its ODT termination resistance<br>available in defining CS0 read<br>command?                                 |

| CONF_CTL_08[63:32] ( | Offset: 0 | x80 |         |                                                                                                                   |

| ODT_WR_MAP_CS3       | 59:56     | 0x0 | 0x0-0xf | Make its ODT termination resistance<br>available in defining CS3 write<br>command?                                |

| ODT_WR_MAP_CS2       | 51:48     | 0x0 | 0x0-0xf | Make its ODT termination resistance available in defining CS2 write                                               |

| <b></b>              | 1         |                   |                                  |                                           |

|----------------------|-----------|-------------------|----------------------------------|-------------------------------------------|

|                      |           |                   |                                  | command?                                  |

|                      |           |                   |                                  | Make its ODT termination resistance       |

| ODT_WR_MAP_CS1       | 43:40     | 0x0               | 0x0-0xf                          | available in defining CS1 write           |

|                      |           |                   |                                  | command?效                                 |

|                      |           |                   |                                  | Make its ODT termination resistance       |

| ODT_WR_MAP_CS0       | 35:32     | 0x0               | 0x0-0xf                          | available in defining CS0 write           |

|                      | 55.52     | 0/10              | ono om                           | command?                                  |

| CONF_CTL_09[31:0] Of | ffset: 02 | v00               |                                  | commune.                                  |

| PORT_DATA_ERROR_ID   |           | $\frac{190}{0x0}$ | $0 \times 0  0 \times f$         | ID number of data amon on the next        |

|                      | 27:24     | 0x0               | 0X0-0X1                          | ID number of data error on the port.      |

| PORT_CMD_ERROR_TY    | 19:16     | 0x0               | 0x0-0xf                          | Type of command errors on port.           |

| PE                   |           |                   |                                  | •••                                       |

| PORT_CMD_ERROR_ID    | 11:8      | 0x0               | 0x0-0xf                          | ID number of command errors on port.      |

| OUT_OF_RANGE_SOUR    | 3:0       | 0x0               | $\Omega v \Omega_{-} \Omega v f$ | ID number of out-of-range access errors.  |

| CE_ID                | 5.0       | 0.00              | 070-071                          | ind number of out-of-range access errors. |

| CONF_CTL_09[63:32] C | Offset: ( | )x90              |                                  |                                           |

|                      |           |                   |                                  | Set OCD pull-up value for memory          |

|                      |           |                   |                                  | chip-select 0. Memory controller will     |

|                      |           |                   |                                  | issue an OCD adjustment command to        |

| OCD_ADJUST_PUP_CS0   | 60:56     | 0x0               | 0x0-0x1f                         | memory module according this              |

|                      |           |                   |                                  | parameter value during initialization     |

|                      |           |                   |                                  |                                           |

|                      |           |                   |                                  | process.                                  |

|                      |           |                   |                                  | Set OCD pull-down value for memory        |

|                      |           |                   |                                  | chip-select 0. Memory controller will     |

| OCD_ADJUST_PDN_CS0   | 52:48     | 0x0               | 0x0-0x1f                         | issue an OCD adjustment command to        |

|                      | 52.10     | 0/10              | ono onn                          | memory module according this              |

|                      |           |                   |                                  | parameter value during initialization     |

|                      |           |                   |                                  | process.                                  |

| TDD                  | 12.10     | 00                | 0x0-0xf                          | Define the number of clock cycles         |

| TRP                  | 43:40     | 0x0               | 0x0-0x1                          | required for memory precharge.            |

|                      |           |                   |                                  | If auto-precharge is set, this parameter  |

| TDAL                 | 35:32     | 0x0               |                                  | defines the number of clock cycles for    |

|                      | 00.02     | 0.10              | 0110 0111                        | auto-precharge and write recovery.        |

| CONF_CTL_10[31:0] Of | ffset: 02 | v a()             |                                  | auto procharge and write recovery.        |

|                      | 1501. 02  | sao -             |                                  | Define initial aging value for the        |

| AGE COUNT            | 29:24     | 00                |                                  | command requeue logic using ageing        |

| AUE_COUNT            | 29:24     | 0x0               | 020-0231                         |                                           |

|                      |           |                   |                                  | algorithm.                                |

|                      | 00.1.5    | 0 0               | 0 0 0 10                         | Define the number of clock cycles         |

| TRC                  | 20:16     | 0x0               | 0x0-0x1f                         | between Active commands to the same       |

|                      |           |                   |                                  | bank.                                     |

|                      |           |                   |                                  | Define the number of clock cycles         |

| TMRD                 | 12:8      | 0x0               | 0x0-0x1f                         | required to configure a mode register     |

|                      |           |                   |                                  | inside memory modules.                    |

| TFAW                 | 4:0       | 0x0               | 0x0-0x1f                         | Define tFAW for memory modules.           |

| CONF_CTL_10[63:32] 0 | Offset: ( | Oxa0              |                                  |                                           |

|                      |           |                   |                                  | Define % of delay for DQS2 when           |

| DLL_DQS_DELAY_2      | 62:56     | 0x0               |                                  | reading data, with an increase of 1/128   |

|                      | 52.50     | 040               | 5A0 0A/1                         | of a clock cycle per time.                |

|                      | I         |                   |                                  | of a clock cycle per tille.               |

\_\_\_\_\_

57

| DLL_DQS_DELAY_1                                                                                                  | 54:48     | 0x0  | 0x0-0x7f  | Define % of delay for DQS1 when<br>reading data, with an increase of 1/128<br>of a clock cycle per time.       |  |  |

|------------------------------------------------------------------------------------------------------------------|-----------|------|-----------|----------------------------------------------------------------------------------------------------------------|--|--|

| DLL_DQS_DELAY_0                                                                                                  | 46:40     | 0x0  | 0x0-0x7f  | Define % of delay for DQS0 when<br>reading data, with an increase of 1/128<br>of a clock cycle per time.       |  |  |

| COMMAND_AGE_COUN<br>T                                                                                            | 37:32     | 0x0  | 0x0-0x3f  | Define initial ageing value for each<br>command when command requeue logic<br>using ageing algorithm.          |  |  |

| CONF_CTL_11[31:0] Offset: 0xb0                                                                                   |           |      |           |                                                                                                                |  |  |

| DLL_DQS_DELAY_6                                                                                                  | 30:24     | 0x0  | 0x0-0x7f  | 1/128 Define % of delay for DQS6<br>when reading data, with an increase of<br>1/128 of a clock cycle per time. |  |  |

| DLL_DQS_DELAY_5                                                                                                  | 22:16     | 0x0  | 0x0-0x7f  | Define % of delay for DQS5 when<br>reading data, with an increase of 1/128<br>of a clock cycle per time.       |  |  |

| DLL_DQS_DELAY_4                                                                                                  | 14:8      | 0x0  | 0x0-0x7f  | Define % of delay for DQS4 when<br>reading data, with an increase of 1/128<br>of a clock cycle per time.       |  |  |

| DLL_DQS_DELAY_3                                                                                                  | 6:0       | 0x0  |           | Define % of delay for DQS3 when<br>reading data, with an increase of 1/128<br>of a clock cycle per time.       |  |  |

| CONF_CTL_11[63:32] C                                                                                             | Offset: ( | Oxb0 |           |                                                                                                                |  |  |

| WR_DQS_SHIFT                                                                                                     | 62:56     | 0x0  | 0x0-0x7f  | Define % of delay for clk_wr when<br>writing data, with an increase of 1/128<br>of a clock cycle per time.     |  |  |

| DQS_OUT_SHIFT                                                                                                    | 54:48     | 0x0  | 0x0-0x7f  | Define % of delay for DQS when<br>writing data, with an increase of 1/128<br>of a clock cycle per time.        |  |  |

| DLL_DQS_DELAY_8                                                                                                  | 46:40     | 0x0  | 0x0-0x7f  | Define % of delay for DQS8 when<br>reading data, with an increase of 1/128<br>of a clock cycle per time.       |  |  |

| DLL_DQS_DELAY_7                                                                                                  | 38:32     | 0x0  | 0x0-0x7f  | Define % of delay for DQS7 when<br>reading data, with an increase of 1/128<br>of a clock cycle per time.       |  |  |

| CONF_CTL_12[31:0] Of                                                                                             | fset: 02  | xc0  |           |                                                                                                                |  |  |

| TRAS_MIN                                                                                                         | 31:24     | 0x0  |           | Define the minimum number of clock<br>cycles for valid row address commands<br>in memory modules.              |  |  |

| OUT_OF_RANGE_LENG<br>TH                                                                                          | 23:16     | 0x0  | 0x0-0xff  | Define command length for out-of-range access.                                                                 |  |  |

| ECC_U_SYND                                                                                                       | 15:8      | 0x0  | 0x0-0xff  | Define the reasons for unrecoverable 2-<br>bit errors (read only).                                             |  |  |

| ECC_C_SYND                                                                                                       | 7:0       | 0x0  | 0x0-0xff  | Define the reasons for recoverable 1-bit errors (read only).                                                   |  |  |

| CONF_CTL_12[63:32] Offset: 0xc0<br>DLL_DQS_DELAY_BYPA 56(48) 0r0 0r1 ff Define the number of dqs0 delay lines in |           |      |           |                                                                                                                |  |  |

| THE DOS DELAY RYPA                                                                                               | 56:48     | 0.0  | 0x0-0x1ff | Define the number of dqs0 delay lines in                                                                       |  |  |

|                                  |           |                             | T                        |                                                                                    |  |  |